# Reference Guide Volume IV -Physical Features

## DRAFT

### PROPRIETARY AND CONFIDENTIAL INFORMATION

**3D***labs*<sup>®</sup>

# Reference Guide Volume IV -Physical Features

### PROPRIETARY AND CONFIDENTIAL INFORMATION

**Issue 1**

The material in this document is the intellectual property of **3D***labs*<sup>®</sup>. It is provided solely for information. You may not reproduce this document in whole or in part by any means. While every care has been taken in the preparation of this document, **3D***labs* accepts no liability for any consequences of its use. Our products are under continual improvement and we reserve the right to change their specification without notice. **3D***labs* may not produce printed versions of each issue of this document. The latest version will be available from the **3D***labs* web site.

**3D***labs* products and technology are protected by a number of worldwide patents. Unlicensed use of any information contained herein may infringe one or more of these patents and may violate the appropriate patent laws and conventions.

**3D***labs*® is the worldwide trading name of **3D***labs* Inc. Ltd.

**3D***labs*, GLINT, GLINT Gamma, PERMEDIA, OXYGEN AND POWERTHREADS are trademarks or registered trademarks of **3D***labs* Ltd., **3D***labs* Inc. Ltd or **3D***labs* Inc.

Microsoft, Windows and Direct3D are either registered trademarks or trademarks of Microsoft Corp. in the United States and/or other countries. OpenGL is a registered trademark of Silicon Graphics, Inc. All other trademarks are acknowledged and recognized.

© Copyright **3D***labs* Inc. Ltd. 1999. All rights reserved worldwide.

Email: info@3dlabs.com Web: http://www.3dlabs.com

**3D***labs* Ltd. Meadlake Place Thorpe Lea Road, Egham Surrey, TW20 8HE United Kingdom Tel: +44 (0) 1784 470555 Fax: +44 (0) 1784 470699 **3D***labs* K.K. Shiroyama JT Mori Bldg 16F 40301 Toranomon Minato-ku, Tokyo, 105, Japan Tel: +81-3-5403-4653 Fax: +91-3-5403-4646

**3D***labs* Inc. 480 Potrero Avenue Sunnyvale, CA 94086, United States Tel: +1 (408) 530-4700 Fax: +1 (408) 530-4701

#### **Change History**

| Document   | Issue | Date        | Change   |

|------------|-------|-------------|----------|

| xxx.3.4 01 | 1     | 11 feb 2002 | Creation |

#### **User Note**

This manual uses hyperlinks (in MSWord DOC file distributions only) to improve ease of access to relevant information for online users. For correct operation of hyperlinks the complete set of *Reference Guide* and *Programmer's Guide* files should be in a single Windows directory or folder.

#### **Table of Contents**

| 7  | PACK    | AGE DIAGRAMS                                                      | 7-1  |

|----|---------|-------------------------------------------------------------------|------|

| 8  | PIN AS  | SIGNMENT                                                          | 8-1  |

|    | 8.1 Co  | nfiguring AGP Pins for PCI boards                                 | 8-1  |

|    | 8.2 Gro | ound and Power Pins                                               | 8-1  |

|    | 8.2.1   | Ground                                                            | 8-1  |

|    | 8.2.2   | VCC2V5 and VDD1V2                                                 | 8-1  |

|    | 8.3 Pin | lists                                                             | 8-2  |

|    | 8.4 Pin | list by Name                                                      | 8-2  |

|    | 8.5 Pin | list by Number                                                    | 8-13 |

|    | 8.6 Scl | nematics                                                          | 8-13 |

| 9  | MEMO    | RY                                                                | 9-1  |

|    | 9.1 Str | obe Setup                                                         | 9-1  |

|    | 9.1.1   | DDR SDRAM                                                         | 9-1  |

|    | 9.1.2   | DDR SGRAM                                                         | 9-2  |

|    | 9.1 Sys | stem Parameters                                                   | 9-2  |

|    | 9.1.1   | Addressing                                                        | 9-2  |

|    | 9.1.2   | Mode and Timing                                                   | 9-2  |

|    | 9.1.3   | Mode                                                              | 9-2  |

|    | 9.1.4   | Extended Mode Parameters                                          | 9-3  |

|    | 9.1.5   | Memory Control                                                    | 9-3  |

|    | 9.1.6   | MVTimingA                                                         | 9-3  |

|    | 9.1.7   | MVTimingB                                                         | 9-4  |

|    | 9.1.8   | MVCaps                                                            | 9-4  |

|    | 9.1.9   | MV0Clock                                                          | 9-5  |

|    | 9.1.10  | MVOS trobeInvert                                                  | 9-5  |

|    | 9.1.11  | MVOS trobeOutDelay{0-1} and MVOS trobeInDelay{0-1} (tQDQSS / tDS) | 9-5  |

| 10 | D RESET | -                                                                 | 10-1 |

| 11 | THER    | /AL                                                               | 11-1 |

|    |         | ermal Performance                                                 | 11-1 |

|    | 11.2 Th | ermal Resistivity Equations                                       | 11-1 |

|    | 11.2.1  | Natural Convection                                                | 11-1 |

|    | 11.2.2  | Forced convection                                                 | 11-2 |

|    | 11.3 Co | oling                                                             | 11-2 |

|    | 11.4 Op | eration with Heatsink                                             | 11-2 |

|    | 11.4.1  | Heatsink Attachment                                               | 11-2 |

|    | 11.4.2  | Calculating cooling requirements                                  | 11-2 |

|    | 11.4.3  | Temperature Range (Commercial/Embedded Applications)              | 11-2 |

| 12 | 2 ELECT |                                                                   | 12-1 |

|    |         | solute Maximum Ratings                                            | 12-1 |

|    |         | Specifications                                                    | 12-1 |

|    | 12.2.1  | PCI Signal DC Specifications                                      | 12-2 |

|    | 12.2.2  | PCI Signal DC Specifications                                      | 12-2 |

|    |         |                                                                   |      |

Proprietary and Confidential

v

| Contents |

|----------|

|----------|

| 12.2.3   | Non-PCI Signal DC Specifications                 | 12-2 |

|----------|--------------------------------------------------|------|

| 12.3 SS  | TL_2 Class I Signals (DDR Memory Interface Only) | 12-2 |

| 12.4 AC  | Specifications                                   | 12-3 |

| 12.4.1   | Clock Timing                                     | 12-3 |

| 12.4.2   | PCI Clock Referenced Input Timing                | 12-3 |

| 12.4.3   | PCI-Referenced Output Timing                     | 12-3 |

| 12.4.4   | AGP Referenced Output Timing                     | 12-4 |

| 12.4.5   | MEMCKOUT Referenced Input and Output Timing      | 12-4 |

| 13 ALERT | S AND ERRATA                                     | 13-2 |

| 13.1 ALE | ERT001                                           | 13-2 |

| 13.1.1   | Problem                                          | 13-2 |

| 13.1.2   | Software Workaround                              | 13-2 |

| 13.2 P9  | ERN001                                           | 13-2 |

| 13.2.1   | Problem                                          | 13-2 |

| 13.2.2   | Software Workaround                              | 13-2 |

| 13.3 P9  | ERN002                                           | 13-2 |

| 13.3.1   | Problem                                          | 13-2 |

| 13.3.2   | Software Workaround                              | 13-2 |

| 13.4 P9  | ERN003                                           | 13-3 |

| 13.4.1   | Problem                                          | 13-3 |

| 13.4.2   | Software Workaround                              | 13-3 |

## **7** Package Diagrams

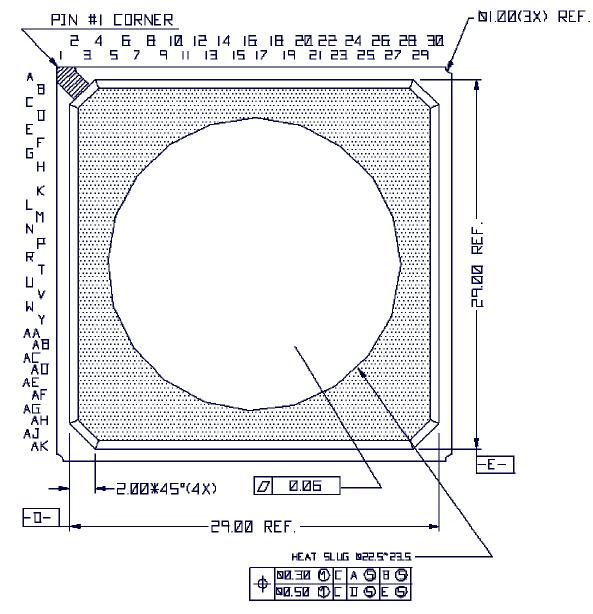

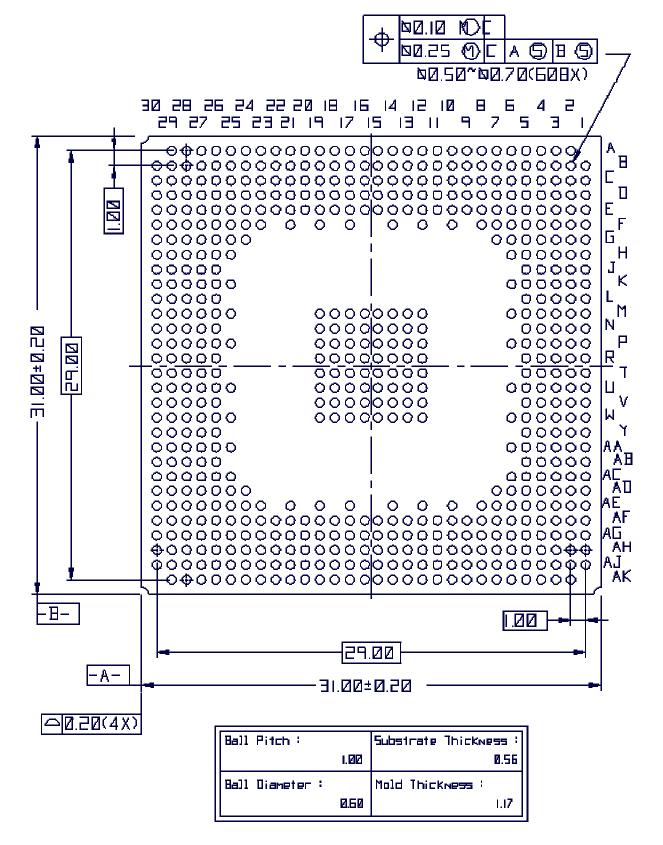

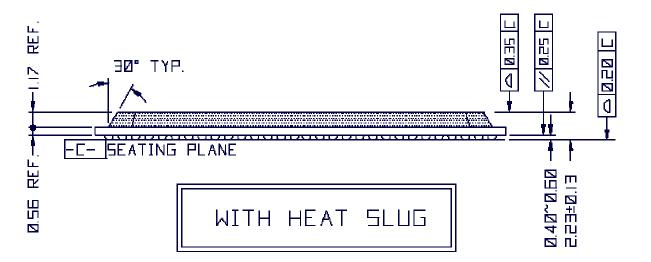

P9 is a 644-ball thermally-enhanced HSBGA package with 100 thermal balls, in a 31mm package.

Figure 7-1 Package Diagram Top View

Figure 7-2 Ball pattern of 644L HSBGA

Figure 7-3 Package Profile Views

| Description      | Dimension      |  |  |

|------------------|----------------|--|--|

| Package Size     | 31.0 x 31.0 mm |  |  |

| Die Size         | 10.7 x 10.7 mm |  |  |

| Туре             | HSBGA          |  |  |

| Body Height      |                |  |  |

| Substrate Layer  | 4L (2 oz)      |  |  |

| Ball pitch       | 1.00 mm        |  |  |

| Ball pad opening | 0.6 mm         |  |  |

Table 7-1 Package dimensions and characteristics

### 8 Pin Assignment

#### 8.1 Configuring AGP Pins for PCI boards

The table below shows pin configuration for AGP pins used in a PCI-bus environment.

| Note: | It is also usually recommended to tie ADSTB and ADSTBN to eliminate possible floating and |

|-------|-------------------------------------------------------------------------------------------|

|       | noise.                                                                                    |

| Pin Name       | Value                                |

|----------------|--------------------------------------|

| AGPSTB         | NC                                   |

| AGPSTBN        | NC                                   |

| AGPSBA[7:0]    | NC                                   |

| AGPST[2:0]     | Pull high to 3.3V with 4.7K resistor |

| AGPADSTB[1:0]  | Pull high to 3.3V with 4.7K resistor |

| AGPADSTBN[1:0] | Pull low to GND with 4.7K resistor   |

| AGPIPEN        | NC                                   |

| AGPRBFN        | NC                                   |

| AGPWBFN        | NC                                   |

| VDDQ[5:0]      | 3.3V Plane                           |

| AGP3V3[4:0]    | 3.3V Plane                           |

| AGPVDet        | GND                                  |

| AGPVref        | Set = PCI voltage/2                  |

| AGPZset        | NC                                   |

#### 8.2 Ground and Power Pins

#### 8.2.1 Ground

At the following pins, Core and I/O ground supply = 0v:

A10, A22, A28, A3, A4, AA25, AA30, AA5, AA6, AB3, AB4, AB5, AC1, AC4, AD5, AE10, AE12, AE14, AE17, AE19, AE21, AE26, AE28, AE5, AE3, AE4, AF10, AF11, AF12, AF13, AF14, AF15, AF18, AF19, AF21, AF22, AF24, AF25, AF26, AG13, AG14, AG27, AG30, AG5, AG3, AG4, AH29, AH30, AH4, AJ14, AJ21, AJ28, AJ3, AJ9, AK20, AK3, AK4, B3, B7, C14, C17, C3, C30, E22, E28, E7, F10, F14, F17, F21, F26, F3, J1, J30, K25, K6, M1, M6, P25, P28, P6, R1, T28, U25, U28, U4, U5, U6, V1, V4, V5, W6, Y3, Y4, Y5.

#### 8.2.2 VCC2V5 and VDD1V2

The following VCC2V5 pins are driven at 2.50vdc nominal:

F5, B1, A2, B2, E5, E8, A9, C12, F12, E15, E16, C19, F19, E23, A24, B26, A29, B30, B29, E26, H30, H26, M28, M25, R26, T26, W28, W25, AB30, AC26, AJ30, AK29, AJ29.

The following VDD1V2 pins are driven at 1.20vdc nominal:

AE6, AD6, AD7, AC6, H6, G6, F6, F7, G7, F8, F23, F24, F25, G25, G24, H25, AC25, AD25, AE25, AE24, AD24, AE23, AE8, AE7.

#### 8.3 Pinlists

The tables below provides a brief description of each pin organized alphabetically by name and numerically by pin number.

All pins are listed here. For specifics of pin electrical characteristics refer to chapter 10, <u>Electrical</u> <u>Characteristics</u>.

The pin type definitions used are:

I/O: Input Signal (tolerates 2.5 and 3.3 VDC PCI and AGP4X standards)

PWR: Various power feed types

BIDIR: Bidirectional signals

IN, OUT Directional signals

Pins added since P10 are shown on a shaded background. There are numerous deletions, reflecting for example the use of only one DDC pair and one Sync pair per head (servicing both DFP and analog ports).

#### 8.4 Pinlist by Name

| PIN NAME     | LOC   | ATION | TYPE  | DESCRIPTION                                             |

|--------------|-------|-------|-------|---------------------------------------------------------|

| AGP3V3[0]    | AK    | 21    | PWR   | 3.30vdc nominal                                         |

| AGP3V3[1]    | AF    | 17    | PWR   | 3.30vdc nominal                                         |

| AGP3V3[2]    | AK    | 28    | PWR   | 3.30vdc nominal                                         |

| AGP3V3[3]    | AK    | 8     | PWR   | 3.30vdc nominal                                         |

| AGP3V3[4]    | AK    | 14    | PWR   | 3.30vdc nominal                                         |

| AGPADSTB[0]  | AJ    | 25    | IN    | AD_STB0 (agp only)                                      |

|              |       |       | IN    | AD_STB0/1# (agp only) AD strobe - used                  |

| AGPADSTB[1]  | AJ    | 17    |       | in agp4x only (1.5v)                                    |

|              |       |       | IN    | AD_STB0/1#(agp only)AD strobe-used in                   |

| AGPADSTBN[0] | AH    | 25    |       | agp4x only[1.5V]                                        |

|              |       |       | IN    | AD_STB0/1#(agp only)AD strobe-used in                   |

| AGPADSTBN[1] | AH    | 17    |       | agp4x only[1.5V]                                        |

|              |       |       | OUT   | PIPE#-Pipelined request(agp only)[3.3V]                 |

| AGPPipeN     | AH    | 10    |       |                                                         |

|              |       |       | BIDIR | RGF# Read buffer full (AGP only) (3.3v)                 |

| AGPRbfN      | AK    | 11    |       |                                                         |

|              |       |       | OUT   | SBA(7:0)-Sideband address port(agp                      |

| AGPSBA[0]    | AJ    | 11    | OUT   | only)[1.5-3.3V]                                         |

|              | A 1 1 | 11    | OUT   | SBA(7-0) sideband address port (agp                     |

| AGPSBA[1]    | AH    | 11    | OUT   | only) (1.5-3.3v)<br>SBA(7-0) sideband address port (agp |

| AGPSBA[2]    | AK    | 12    | 001   | only) (1.5-3.3v)                                        |

|              | /     | 12    | OUT   | SBA(7-0) sideband address port (agp                     |

| AGPSBA[3]    | AG    | 11    | 001   | only) (1.5-3.3v)                                        |

|              |       |       | OUT   | SBA(7:0)-Sideband address port(agp                      |

| AGPSBA[4]    | AK    | 13    |       | only)[1.5-3.3V]                                         |

|              |       |       | OUT   | SBA(7:0)-Sideband address port(agp                      |

| AGPSBA[5]    | AG    | 12    |       | only)[1.5-3.3V]                                         |

|              |       |       | OUT   | SBA(7:0)-Sideband address port(agp                      |

| AGPSBA[6]    | AJ    | 13    |       | only)[1.5-3.3V]                                         |

|              |       |       | OUT   | SBA(7:0)-Sideband address port(agp                      |

| AGPSBA[7]    | AH    | 13    |       | only)[1.5-3.3V]                                         |

| PIN NAME   | LOCATION |    | TYPE  | DESCRIPTION                                              |  |

|------------|----------|----|-------|----------------------------------------------------------|--|

|            |          |    | OUT   | SB_STB Sideband strobe (agp only)-                       |  |

| AGPSBSTB   | AJ       | 12 |       | (differential in AGP4x)[1.5V-3.3V]                       |  |

|            |          |    | OUT   | SB_STB# Sideband strobe (agp only)                       |  |

|            |          |    |       | differential strobe used in agp4x only                   |  |

| AGPSBSTBN  | AH       | 12 |       | (1.5v).                                                  |  |

| AGPSt[0]   | AK       | 10 | BIDIR | ST Status bus (agp only) (1.5-3.3v)                      |  |

| AGPSt[1]   | AG       | 9  | BIDIR | ST Status bus(agp only)[3.3V]                            |  |

| AGPSt[2]   | AJ       | 10 | BIDIR | ST Status bus (agp only) [3.3V]                          |  |

|            |          |    | BIDIR | AGP I/O Reference voltage = VCCA 15/2                    |  |

| AGPVREF    | AK       | 27 |       | (1.67v or 0.75v)                                         |  |

| AGPWbfN    | AG       | 10 | IN    | Write Buffer Full signal                                 |  |

|            |          |    | IN    | Analog reference impedance(resistor)-                    |  |

| AGPZSET    | AF       | 20 |       | connect to VDDQ via 37.5 ohms                            |  |

|            |          | 2  | PWR   | DAC Head 0 analogue ground = $0v$                        |  |

| DacAAG[0]  | AH       | 3  | PWR   | (isolated from GND)<br>DAC Head 0 Analogue Ground        |  |

| DacAAG[1]  | AG       | 2  | PWR   |                                                          |  |

| DacAAG[2]  | AD       | 2  | PWR   | DAC Head 0 Analogue Ground<br>DAC Head 0 Analogue Ground |  |

| DacAAG[3]  | AD       | 4  | AN    | DAC Head 0 Blue Out                                      |  |

| DacABlue   | AD       | 1  | AN    | DAC Head 0 Op-amp Compensation                           |  |

| DacAComp   | AE       | 1  | AN    | DAC Head 0 Op-amp Compensation                           |  |

| DacAFSAdj  | AD       | 3  | AN    | DAC Head 0 Full Scale Adjust                             |  |

| DacAGreen  | AF       | 1  | AN    | DAC Head 0 Green Out                                     |  |

| DacARed    | AG       | 1  | OUT   | DAC Head 0 Red Out                                       |  |

| DacAVAA[0] | AF       | 2  | PWR   | DAC Head 0 Analogue Power                                |  |

| DacAVAA[0] | AF       | 4  | PWR   | DAC Head 0 Analogue Power                                |  |

| DacAVAA[1] | AE       | 2  | PWR   | DAC Head 0 Analogue Power                                |  |

| Dachthh[2] |          | 2  | PWR   | DAC Head 0 Voltage Reference signal                      |  |

| DacAVref   | AF       | 3  |       |                                                          |  |

| DacBAG[0]  | AC       | 3  | PWR   | DAC Head 1 Analogue Ground                               |  |

| DacBAG[1]  | AB       | 2  | PWR   | DAC Head 1 Analogue Ground                               |  |

| DacBAG[2]  | W        | 2  | PWR   | DAC Head 1 Analogue Ground                               |  |

| DacBAG[3]  | W        | 4  | PWR   | DAC Head 1 Analogue Ground                               |  |

| DacBBlue   | W        | 1  | AN    | DAC Head 1 Blue Out                                      |  |

|            |          |    | AN    | DAC Head 1 Op-amp Compensation                           |  |

| DacBComp   | Y        | 1  |       |                                                          |  |

| DacBFSAdj  | W        | 3  | AN    | DAC Head 1 Full Scale Adjust                             |  |

| DacBGreen  | AA       | 1  | AN    | DAC Head 1 Green Out                                     |  |

| DacBRed    | AB       | 1  | AN    | DAC Head 1 Red Out                                       |  |

| DacBVAA[0] | AA       | 2  | PWR   | DAC Head 1 Analogue Power                                |  |

| DacBVAA[1] | AA       | 4  | PWR   | DAC Head 1 Analogue Power                                |  |

| DacBVAA[2] | Y        | 2  | PWR   | DAC Head 1 Analogue Power                                |  |

| DacBVref   | AA       | 3  | PWR   | DAC Head 1 Voltage Reference                             |  |

| DfpABlank  | к        | 1  | OUT   | DFP Blank signal Head 0                                  |  |

| DfpAStrobe | J        | 5  | OUT   | DFP Data Strobe signal Head 0                            |  |

| DfpBBlank  | N        | 2  | OUT   | DFP Blank signal Head 1                                  |  |

| DfpBStrobe | N        | 1  | OUT   | DFP Strobe signal Head 1                                 |  |

|            |          |    | BIDIR | Flat Panel Data signal / Interleave Data In              |  |

| DfpData[0] | F        | 2  |       | signal                                                   |  |

| PIN NAME                | LOCATIO  | N TYPE | DESCRIPTION                                           |

|-------------------------|----------|--------|-------------------------------------------------------|

|                         | _        | BIDIR  | Flat Panel Data signal / Interleave Data In           |

| DfpData[1]              | F 1      |        | signal                                                |

|                         |          | BIDIR  | Flat Panel Data signal / Interleave Data In           |

| DfpData[10]             | J 3      |        | signal                                                |

|                         |          | BIDIR  | Flat Panel Data signal / Interleave Data In           |

| DfpData[11]             | J 4      |        | signal                                                |

|                         |          | BIDIR  | Flat Panel Data signal / Interleave Data In           |

| DfpData[12]             | K 2      |        | signal                                                |

| D(+ D + (-140)          |          | BIDIR  | Flat Panel Data signal / Interleave Data In           |

| DfpData[13]             | K 3      | סוסוס  | signal                                                |

| DfpData[14]             | К 4      | BIDIR  | Flat Panel Data signal / Interleave Data In           |

| DfpData[14]             | <u> </u> | BIDIR  | signal<br>Flat Panel Data signal / Interleave Data In |

| DfpData[15]             | L 1      | DIDIK  | signal                                                |

| DipDala[15]             |          | BIDIR  | Flat Panel Data signal / Interleave Data In           |

| DfpData[16]             | L 2      | DIDIK  | signal                                                |

|                         |          | BIDIR  | Flat Panel Data signal / Interleave Data In           |

| DfpData[17]             | L 3      | DIDIIX | signal                                                |

| Dipbata[11]             |          | BIDIR  | Flat Panel Data signal / Interleave Data In           |

| DfpData[18]             | L 4      | DIDIN  | signal                                                |

| DipBala[10]             |          | BIDIR  | Flat Panel Data signal / Interleave Data In           |

| DfpData[19]             | L 5      | 2.2    | signal                                                |

| _ · [ - • · • · [ · • ] |          | BIDIR  | Flat Panel Data signal / Interleave Data In           |

| DfpData[2]              | G 2      |        | signal                                                |

|                         |          | BIDIR  | Flat Panel Data signal / Interleave Data In           |

| DfpData[20]             | M 2      |        | signal                                                |

| - <b>· ·</b>            |          | BIDIR  | Flat Panel Data signal / Interleave Data In           |

| DfpData[21]             | М 3      |        | signal                                                |

|                         |          | BIDIR  | Flat Panel Data signal / Interleave Data In           |

| DfpData[22]             | M 4      |        | signal                                                |

|                         |          | BIDIR  | Flat Panel Data signal / Interleave Data In           |

| DfpData[23]             | M 5      |        | signal                                                |

|                         |          | BIDIR  | Flat Panel Data signal / Interleave Data In           |

| DfpData[3]              | G 3      |        | signal                                                |

|                         |          | BIDIR  | Flat Panel Data signal / Interleave Data In           |

| DfpData[4]              | G 4      |        | signal                                                |

|                         |          | BIDIR  | Flat Panel Data signal / Interleave Data In           |

| DfpData[5]              | H 1      |        | signal                                                |

|                         |          | BIDIR  | Flat Panel Data signal / Interleave Data In           |

| DfpData[6]              | H 2      |        | signal                                                |

|                         |          | BIDIR  | Flat Panel Data signal / Interleave Data In           |

| DfpData[7]              | H 3      |        | signal                                                |

| Df= D =t=[0]            |          | BIDIR  | Flat Panel Data signal / Interleave Data In           |

| DfpData[8]              | H 4      | BIDIR  | signal<br>Flat Panel Data signal / Interleave Data In |

| DfpData[9]              | Н 5      | JUIK   | signal                                                |

| DipData[9]              |          | PWR    | Supplied from SSTLDFP_Vref =                          |

| DFPVREF[0]              | J 2      |        | VCC_DFP/2                                             |

|                         |          | PWR    | Supplied from SSTLDFP_Vref =                          |

| DFPVREF[1]              | N 3      |        | VCC_DFP/2                                             |

|                         |          | IN     | Genlock Vertical Sync signal for                      |

|                         |          |        | ExtVSync, enabled by GenLockControl                   |

| GenVSync                | AG 7     |        | register                                              |

| PIN NAME   | LOC | LOCATION |       | DESCRIPTION                                                        |  |

|------------|-----|----------|-------|--------------------------------------------------------------------|--|

| Lock       | AG  | 6        | BIDIR | Same as P10 VidLock signals                                        |  |

| MAAddr[10] | А   | 18       | OUT   | Memory Controller A Address signal                                 |  |

| MAAddr[0]  | В   | 13       | OUT   | Memory Controller A Address signal                                 |  |

| MAAddr[1]  | А   | 15       | OUT   | Memory Controller A Address signal                                 |  |

| MAAddr[2]  | В   | 17       | OUT   | Memory Controller A Address signal                                 |  |

| MAAddr[3]  | В   | 18       | OUT   | Memory Controller A Address signal                                 |  |

| MAAddr[4]  | А   | 19       | OUT   | Memory Controller A Address signal                                 |  |

| MAAddr[5]  | В   | 19       | OUT   | Memory Controller A Address signal                                 |  |

| MAAddr[6]  | В   | 20       | OUT   | Memory Controller A Address signal                                 |  |

| MAAddr[7]  | A   | 17       | OUT   | Memory Controller A Address signal                                 |  |

| MAAddr[8]  | А   | 14       | OUT   | Memory Controller A Address signal                                 |  |

| MAAddr[9]  | В   | 15       | OUT   | Memory Controller A Address signal                                 |  |

|            |     |          | OUT   | Memory Controller A Address 'A' signal                             |  |

| MAAddrA    | В   | 14       |       |                                                                    |  |

|            |     |          | BIDIR | Memory Controller A Address 'B' signal                             |  |

| MAAddrB[0] | A   | 16       |       |                                                                    |  |

|            |     |          | OUT   | Memory Controller A Address 'B' signal                             |  |

| MAAddrB[1] | В   | 16       | OUT   |                                                                    |  |

|            | в   | 12       | OUT   | Memory Controller A Bank Address signal                            |  |

| MABa[0]    | В   | 12       | OUT   | Memory Controller A Bank Address signal                            |  |

| MABa[1]    | A   | 13       | 001   | Memory Controller A Darik Address signal                           |  |

|            |     |          | OUT   | Memory Controller A Column Address                                 |  |

| MACasN     | В   | 11       |       | Strobe signal                                                      |  |

|            |     |          | OUT   | Memory Controller A Clock Enable signal                            |  |

| MACke      | В   | 21       |       |                                                                    |  |

|            |     |          | OUT   | Memory Controller A Differential Clock                             |  |

| MACIk      | Α   | 20       |       | signal                                                             |  |

| MACHINI    |     | 04       | OUT   | Memory Controller A Differential Clock                             |  |

|            | A   | 21       | BIDIR | signal                                                             |  |

| MAData[0]  | F   | 4        | BIDIR | Memory Controller A Data signal                                    |  |

| MAData[1]  | E   | 4        |       | Memory Controller A Data signal<br>Memory Controller A Data signal |  |

| MAData[10] | B   | 4        | BIDIR |                                                                    |  |

| MAData[11] | D   | 5        | BIDIR | Memory Controller A Data signal                                    |  |

| MAData[12] | C   | 5        |       | Memory Controller A Data signal                                    |  |

| MAData[13] | B   | 5        | BIDIR | Memory Controller A Data signal                                    |  |

| MAData[14] | A   | 5        | BIDIR | Memory Controller A Data signal                                    |  |

| MAData[15] | E   | 6        | BIDIR | Memory Controller A Data signal                                    |  |

| MAData[16] | D   | 6        | BIDIR | Memory Controller A Data signal                                    |  |

| MAData[17] | С   | 6        | BIDIR | Memory Controller A Data signal                                    |  |

| MAData[18] | D   | 7        | BIDIR | Memory Controller A Data signal                                    |  |

| MAData[19] | C   | 7        | BIDIR | Memory Controller A Data signal                                    |  |

| MAData[2]  | E   | 3        | BIDIR | Memory Controller A Data signal                                    |  |

| MAData[20] | A   | 7        | BIDIR | Memory Controller A Data signal                                    |  |

| MAData[21] | D   | 8        | BIDIR | Memory Controller A Data signal                                    |  |

| MAData[22] | С   | 8        | BIDIR | Memory Controller A Data signal                                    |  |

| MAData[23] | E   | 9        | BIDIR | Memory Controller A Data signal                                    |  |

| MAData[24] | D   | 9        | BIDIR | Memory Controller A Data signal                                    |  |

| MAData[25] | С   | 9        | BIDIR | Memory Controller A Data signal                                    |  |

| MAData[26] | В   | 9        | BIDIR | Memory Controller A Data signal                                    |  |

| PIN NAME   | LOCA   | TION | TYPE  | DESCRIPTION                                                       |

|------------|--------|------|-------|-------------------------------------------------------------------|

| MAData[27] | E      | 10   | BIDIR | Memory Controller A Data signal                                   |

| MAData[28] | D      | 10   | BIDIR | Memory Controller A Data signal                                   |

| MAData[29] | с      | 10   | BIDIR | Memory Controller A Data signal                                   |

| MAData[3]  | E      | 2    | BIDIR | Memory Controller A Data signal                                   |

| MAData[30] | Е      | 11   | BIDIR | Memory Controller A Data signal                                   |

| MAData[31] | E      | 12   | BIDIR | Memory Controller A Data signal                                   |

| MAData[32] | D      | 12   | BIDIR | Memory Controller A Data signal                                   |

| MAData[33] | E      | 13   | BIDIR | Memory Controller A Data signal                                   |

| MAData[34] | _<br>D | 13   | BIDIR | Memory Controller A Data signal                                   |

| MAData[35] | C      | 13   | BIDIR | Memory Controller A Data signal                                   |

| MAData[36] | E      | 14   | BIDIR | Memory Controller A Data signal                                   |

| MAData[37] | D      | 14   | BIDIR | Memory Controller A Data signal                                   |

| MAData[38] | D      | 15   | BIDIR | Memory Controller A Data signal                                   |

| MAData[39] | c      | 15   | BIDIR | Memory Controller A Data signal                                   |

| MAData[4]  | E      | 1    | BIDIR | Memory Controller A Data signal                                   |

| MAData[40] | E      | 17   | BIDIR | Memory Controller A Data signal                                   |

| MAData[41] | D      | 17   | BIDIR | Memory Controller A Data signal                                   |

| MAData[42] | E      | 18   | BIDIR | Memory Controller A Data signal                                   |

| MAData[43] | D      | 18   | BIDIR | Memory Controller A Data signal                                   |

| MAData[44] | C      | 18   | BIDIR | Memory Controller A Data signal                                   |

| MAData[45] | E      | 19   | BIDIR | Memory Controller A Data signal                                   |

|            | D      | 19   | BIDIR | Memory Controller A Data signal                                   |

| MAData[46] | E      | 20   | BIDIR | Memory Controller A Data signal                                   |

| MAData[47] | E      | 20   | BIDIR | Memory Controller A Data signal                                   |

| MAData[48] | ⊑<br>D | 21   | BIDIR | Memory Controller A Data signal                                   |

| MAData[49] | D      | 3    | BIDIR | Memory Controller A Data signal                                   |

| MAData[5]  | С      | 21   | BIDIR | Memory Controller A Data signal                                   |

| MAData[50] | D      | 22   | BIDIR | Memory Controller A Data signal                                   |

| MAData[51] | C      | 22   | BIDIR | Memory Controller A Data signal                                   |

| MAData[52] |        |      | BIDIR | Memory Controller A Data signal                                   |

| MAData[53] | D      | 23   | BIDIR | Memory Controller A Data signal                                   |

| MAData[54] | C      | 23   | BIDIR | Memory Controller A Data signal                                   |

| MAData[55] | E      | 24   | BIDIR | Memory Controller A Data signal                                   |

| MAData[56] | D      | 24   | BIDIR | Memory Controller A Data signal                                   |

| MAData[57] | C      | 24   | BIDIR | Memory Controller A Data signal                                   |

| MAData[58] | B      | 24   |       | , ,                                                               |

| MAData[59] | E      | 25   | BIDIR | Memory Controller A Data signal                                   |

| MAData[6]  | С      | 2    | BIDIR | Memory Controller A Data signal                                   |

| MAData[60] | D      | 25   | BIDIR | Memory Controller A Data signal                                   |

| MAData[61] | С      | 25   | BIDIR | Memory Controller A Data signal                                   |

| MAData[62] | D      | 26   | BIDIR | Memory Controller A Data signal                                   |

| MAData[63] | C      | 26   | BIDIR | Memory Controller A Data signal                                   |

| MAData[7]  | С      | 1    | BIDIR | Memory Controller A Data signal                                   |

| MAData[8]  | D      | 4    | BIDIR | Memory Controller A Data signal                                   |

| MAData[9]  | С      | 4    | BIDIR | Memory Controller A Data signal<br>Memory controller A Data write |

| MADm[0]    | D      | 2    | OUT   | mask signal                                                       |

| MADm[1]    | в      | 6    | OUT   | Memory controller A Data write<br>mask signal                     |

| MADm[2]    | в      | 8    | OUT   | Memory controller A Data write                                    |

| PIN NAME   | LOCATIO | ON TYPE                               | DESCRIPTION                                   |  |

|------------|---------|---------------------------------------|-----------------------------------------------|--|

|            |         |                                       | mask signal                                   |  |

|            |         |                                       | Memory controller A Data write                |  |

| MADm[3]    | D 11    | OUT                                   | mask signal                                   |  |

|            | D 16    | OUT                                   | Memory controller A Data write<br>mask signal |  |

| MADm[4]    |         | 001                                   | Memory controller A Data write                |  |

| MADm[5]    | D 20    | OUT                                   | mask signal                                   |  |

|            |         |                                       | Memory controller A Data write                |  |

| MADm[6]    | B 23    | OUT                                   | mask signal<br>Memory controller A Data write |  |

| MADm[7]    | B 25    | OUT                                   | mask signal                                   |  |

|            |         | BIDIR                                 | Memory Controller A Data Strobe signal        |  |

| MADqs[0]   | D 1     |                                       |                                               |  |

|            |         | BIDIR                                 | Memory Controller A Data Strobe signal        |  |

| MADqs[1]   | A 6     |                                       |                                               |  |

| MADqs[2]   | A 8     | BIDIR                                 | Memory Controller A Data Strobe signal        |  |

| MADQS[2]   | A 0     | BIDIR                                 | Memory Controller A Data Strobe signal        |  |

| MADqs[3]   | C 11    |                                       | Mornery Controller / Data Otrobe Signal       |  |

| 1-1-1      |         | BIDIR                                 | Memory Controller A Data Strobe signal        |  |

| MADqs[4]   | C 16    |                                       |                                               |  |

|            |         | BIDIR                                 | Memory Controller A Data Strobe signal        |  |

| MADqs[5]   | C 20    |                                       |                                               |  |

|            |         | BIDIR                                 | Memory Controller A Data Strobe signal        |  |

| MADqs[6]   | A 23    | BIDIR                                 | Memory Controller A Data Strobe signal        |  |

| MADqs[7]   | A 25    |                                       |                                               |  |

|            |         | OUT                                   | Memory Controller A Row Address Strobe        |  |

| MARasN     | A 12    |                                       | signal                                        |  |

|            |         | OUT                                   | Memory Controller A Write Enable signal       |  |

| MAWeN      | A 11    |                                       |                                               |  |

| MBAddr[10] | U 30    |                                       | Memory Controller B Address signal            |  |

| MBAddr[0]  | M 29    |                                       | Memory Controller B Address signal            |  |

| MBAddr[1]  | P 30    | - · · · -                             | Memory Controller B Address signal            |  |

| MBAddr[2]  | T 29    |                                       | Memory Controller B Address signal            |  |

| MBAddr[3]  | U 29    | - · · ·                               | Memory Controller B Address signal            |  |

| MBAddr[4]  | V 30    | a                                     | Memory Controller B Address signal            |  |

| MBAddr[5]  | V 29    | - · · · -                             | Memory Controller B Address signal            |  |

| MBAddr[6]  | W 29    | - · · · -                             | Memory Controller B Address signal            |  |

| MBAddr[7]  | T 30    | o                                     | Memory Controller B Address signal            |  |

| MBAddr[8]  | N 30    |                                       | Memory Controller B Address signal            |  |

| MBAddr[9]  | P 29    |                                       | Memory Controller B Address signal            |  |

| MBAddrA    | N 29    | OUT                                   | Memory Controller B Address 'A' signal        |  |

|            | 29      | OUT                                   | Memory Controller B Address 'B' signal        |  |

| MBAddrB[0] | R 30    |                                       |                                               |  |

|            |         | OUT                                   | Memory Controller B Address 'B' signal        |  |

| MBAddrB[1] | R 29    | · · · · · · · · · · · · · · · · · · · |                                               |  |

|            |         | OUT                                   | Memory Controller B Bank Address signal       |  |

| MBBa[0]    | L 29    |                                       |                                               |  |

|            |         | OUT                                   | Memory Controller B Bank Address signal       |  |

| MBBa[1]    | M 30    |                                       |                                               |  |

| PIN NAME L |     | LOCATION |       | DESCRIPTION                                      |

|------------|-----|----------|-------|--------------------------------------------------|

|            |     |          | OUT   | Memory Controller B Column Address               |

| MBCasN     | к   | 29       |       | Strobe signal                                    |

|            |     |          | OUT   | Memory Controller B Clock Enable signal          |

| MBCke      | Y   | 29       | 0.17  |                                                  |

| MDOIL      | 10/ | 20       | OUT   | Memory Controller B Differential Clock           |

| MBClk      | W   | 30       | OUT   | signal<br>Memory Controller B Differential Clock |

| MBCIkN     | Y   | 30       | 001   | signal                                           |

| MBData[0]  | A   | 26       | BIDIR | Memory Controller B Data signal                  |

| MBData[1]  | C   | 27       | BIDIR | Memory Controller B Data signal                  |

| MBData[10] | F   | 27       | BIDIR | Memory Controller B Data signal                  |

| MBData[11] | F   | 28       | BIDIR | Memory Controller B Data signal                  |

| MBData[12] | F   | 29       | BIDIR | Memory Controller B Data signal                  |

| MBData[13] | F   | 30       | BIDIR | Memory Controller B Data signal                  |

| MBData[14] | G   | 26       | BIDIR | Memory Controller B Data signal                  |

| MBData[15] | G   | 27       | BIDIR | Memory Controller B Data signal                  |

| MBData[16] | G   | 28       | BIDIR | Memory Controller B Data signal                  |

| MBData[17] | G   | 29       | BIDIR | Memory Controller B Data signal                  |

| MBData[18] | G   | 30       | BIDIR | Memory Controller B Data signal                  |

| MBData[19] | H   | 27       | BIDIR | Memory Controller B Data signal                  |

| MBData[2]  | В   | 28       | BIDIR | Memory Controller B Data signal                  |

| MBData[20] | H   | 28       | BIDIR | Memory Controller B Data signal                  |

| MBData[21] | Н   | 29       | BIDIR | Memory Controller B Data signal                  |

| MBData[22] | J   | 26       | BIDIR | Memory Controller B Data signal                  |

| MBData[23] | ĸ   | 26       | BIDIR | Memory Controller B Data signal                  |

| MBData[24] | К   | 27       | BIDIR | Memory Controller B Data signal                  |

| MBData[25] | K   | 28       | BIDIR | Memory Controller B Data signal                  |

| MBData[26] | 1   | 26       | BIDIR | Memory Controller B Data signal                  |

| MBData[27] | M   | 26       | BIDIR | Memory Controller B Data signal                  |

| MBData[28] | M   | 27       | BIDIR | Memory Controller B Data signal                  |

| MBData[29] | N   | 26       | BIDIR | Memory Controller B Data signal                  |

| MBData[3]  | C   | 28       | BIDIR | Memory Controller B Data signal                  |

| MBData[30] | N   | 27       | BIDIR | Memory Controller B Data signal                  |

| MBData[31] | N   | 28       | BIDIR | Memory Controller B Data signal                  |

| MBData[32] | P   | 26       | BIDIR | Memory Controller B Data signal                  |

| MBData[33] | P   | 27       | BIDIR | Memory Controller B Data signal                  |

| MBData[34] | T   | 27       | BIDIR | Memory Controller B Data signal                  |

| MBData[35] | U   | 26       | BIDIR | Memory Controller B Data signal                  |

| MBData[36] | U   | 27       | BIDIR | Memory Controller B Data signal                  |

| MBData[37] | V   | 26       | BIDIR | Memory Controller B Data signal                  |

| MBData[38] | V   | 27       | BIDIR | Memory Controller B Data signal                  |

| MBData[39] | V   | 28       | BIDIR | Memory Controller B Data signal                  |

| MBData[33] | C   | 29       | BIDIR | Memory Controller B Data signal                  |

| MBData[4]  | w   | 29       | BIDIR | Memory Controller B Data signal                  |

| MBData[40] | W   | 20       | BIDIR | Memory Controller B Data signal                  |

| MBData[41] | Y   | 26       | BIDIR | Memory Controller B Data signal                  |

|            | AA  | 26       | BIDIR | Memory Controller B Data signal                  |

| MBData[43] |     |          | BIDIR | Memory Controller B Data signal                  |

| MBData[44] | AA  | 27       | BIDIR | Memory Controller B Data signal                  |

| MBData[45] | AA  | 28       | אוסוס | Merriory Controller & Data Signal                |

| PIN NAME   | LOCA  | ATION | TYPE     | DESCRIPTION                                                       |  |  |

|------------|-------|-------|----------|-------------------------------------------------------------------|--|--|

| MBData[46] | AB    | 26    | BIDIR    | Memory Controller B Data signal                                   |  |  |

| MBData[47] | AB    | 27    | BIDIR    | Memory Controller B Data signal                                   |  |  |

| MBData[48] | AB    | 28    | BIDIR    | Memory Controller B Data signal                                   |  |  |

| MBData[49] | AB    | 29    | BIDIR    | Memory Controller B Data signal                                   |  |  |

| MBData[5]  | D     | 27    | BIDIR    | Memory Controller B Data signal                                   |  |  |

| MBData[50] | AC    | 27    | BIDIR    | Memory Controller B Data signal                                   |  |  |

| MBData[51] | AC    | 28    | BIDIR    | Memory Controller B Data signal                                   |  |  |

| MBData[52] | AD    | 26    | BIDIR    | Memory Controller B Data signal                                   |  |  |

| MBData[53] | AD    | 27    | BIDIR    | Memory Controller B Data signal                                   |  |  |

| MBData[54] | AD    | 28    | BIDIR    | Memory Controller B Data signal                                   |  |  |

| MBData[55] | AD    | 29    | BIDIR    | Memory Controller B Data signal                                   |  |  |

| MBData[56] | AD    | 30    | BIDIR    | Memory Controller B Data signal                                   |  |  |

| MBData[57] | AE    | 27    | BIDIR    | Memory Controller B Data signal                                   |  |  |

| MBData[58] | AE    | 29    | BIDIR    | Memory Controller B Data signal                                   |  |  |

| MBData[59] | AE    | 30    | BIDIR    | Memory Controller B Data signal                                   |  |  |

| MBData[6]  | D     | 28    | BIDIR    | Memory Controller B Data signal                                   |  |  |

|            | AF    | 27    | BIDIR    | Memory Controller B Data signal                                   |  |  |

| MBData[60] | AF    | 28    | BIDIR    | Memory Controller B Data signal                                   |  |  |

| MBData[61] |       |       | BIDIR    | Memory Controller B Data signal                                   |  |  |

| MBData[62] | AG    | 28    | BIDIR    | Memory Controller B Data signal                                   |  |  |

| MBData[63] | AG    | 29    | BIDIR    |                                                                   |  |  |

| MBData[7]  | D     | 29    |          | Memory Controller B Data signal                                   |  |  |

| MBData[8]  | D     | 30    | BIDIR    | Memory Controller B Data signal                                   |  |  |

| MBData[9]  | E     | 27    |          | Memory Controller B Data signal<br>Memory Controller B Data wirte |  |  |

| MBDm[0]    | в     | 27    | 001      | mask signal                                                       |  |  |

|            |       |       | OUT      | Memory Controller B Data wirte                                    |  |  |

| MBDm[1]    | E     | 29    |          | mask signal                                                       |  |  |

| MBDm[2]    |       | 27    | OUT      | Memory Controller B Data wirte<br>mask signal                     |  |  |

|            | J     | 21    | OUT      | Memory Controller B Data wirte                                    |  |  |

| MBDm[3]    | L     | 27    |          | mask signal                                                       |  |  |

|            |       |       | OUT      | Memory Controller B Data wirte                                    |  |  |

| MBDm[4]    | R     | 27    | OUT      | mask signal<br>Memory Controller B Data wirte                     |  |  |

| MBDm[5]    | Y     | 27    | 001      | mask signal                                                       |  |  |

|            |       |       | OUT      | Memory Controller B Data wirte                                    |  |  |

| MBDm[6]    | AC    | 29    | <u> </u> | mask signal                                                       |  |  |

|            |       |       | OUT      | Memory Controller B Data wirte<br>mask signal                     |  |  |

| MBDm[7]    | AF    | 29    | BIDIR    | Memory Controller B Data Strobe signal                            |  |  |

| MBDqs[0]   | А     | 27    | DIDIK    | Meriory Controller & Data Strobe Signal                           |  |  |

|            | ~~~~~ | 21    | BIDIR    | Memory Controller B Data Strobe signal                            |  |  |

| MBDqs[1]   | E     | 30    | 2.2      |                                                                   |  |  |

|            |       |       | BIDIR    | Memory Controller B Data Strobe signal                            |  |  |

| MBDqs[2]   | J     | 28    |          |                                                                   |  |  |

|            |       |       | BIDIR    | Memory Controller B Data Strobe signal                            |  |  |

| MBDqs[3]   | L     | 28    |          |                                                                   |  |  |

|            |       |       | BIDIR    | Memory Controller B Data Strobe signal                            |  |  |

| MBDqs[4]   | R     | 28    | B.F. :-  |                                                                   |  |  |

| MDDariel   |       | 00    | BIDIR    | Memory Controller A Data Strobe signal                            |  |  |

| MBDqs[5]   | Y     | 28    |          |                                                                   |  |  |

| PIN NAME  | LOC | LOCATION |       | DESCRIPTION                                          |  |  |

|-----------|-----|----------|-------|------------------------------------------------------|--|--|

|           | AC  | AC 30    |       | Memory Controller B Data Strobe signal               |  |  |

| MBDqs[7]  | AF  | 30       | BIDIR | Memory Controller B Data Strobe signal               |  |  |

| MBRasN    | L   | 30       | OUT   | Memory Controller B Row Address Strobe signal        |  |  |

|           |     |          | OUT   | Memory Controller B Write Enable signal              |  |  |

| MBWeN     | К   | 30       | BIDIR | AD(31-0) address and data bus (1.5-3.3V)             |  |  |

| PCIAD[0]  | AH  | 27       | BIDIR | AD(31-0) address and data bus (1.5-3.3V)             |  |  |

| PCIAD[1]  | AJ  | 27       | סוסוס | $\Delta D(24,0)$ address and data hus $(4.5,2,2)(1)$ |  |  |

| PCIAD[10] | AJ  | 24       | BIDIR | AD(31-0) address and data bus (1.5-3.3V)             |  |  |

| PCIAD[11] | AG  | 23       | BIDIR | AD(31-0) address and data bus (1.5-3.3V)             |  |  |

| PCIAD[12] | AK  | 23       | BIDIR | AD(31-0) address and data bus (1.5-3.3V)             |  |  |

|           |     | 23       | BIDIR | AD(31-0) address and data bus (1.5-3.3V)             |  |  |

| PCIAD[13] | AH  |          | BIDIR | AD(31-0) address and data bus (1.5-3.3V)             |  |  |

| PCIAD[14] | AJ  | 23       | BIDIR | AD(31-0) address and data bus (1.5-3.3V)             |  |  |

| PCIAD[15] | AG  | 22       | BIDIR | AD(31-0) address and data bus (1.5-3.3V)             |  |  |

| PCIAD[16] | AG  | 19       | BIDIR | AD(31-0) address and data bus (1.5-3.3V)             |  |  |

| PCIAD[17] | AJ  | 19       |       |                                                      |  |  |

| PCIAD[18] | AH  | 19       | BIDIR | AD(31-0) address and data bus (1.5-3.3V)             |  |  |

| PCIAD[19] | AK  | 18       | BIDIR | AD(31-0) address and data bus (1.5-3.3V)             |  |  |

| PCIAD[2]  | AG  | 26       | BIDIR | AD(31-0) address and data bus (1.5-3.3V)             |  |  |

|           |     |          | BIDIR | AD(31-0) address and data bus (1.5-3.3V)             |  |  |

| PCIAD[20] | AG  | 18       | BIDIR | AD(31-0) address and data bus (1.5-3.3V)             |  |  |

| PCIAD[21] | AJ  | 18       | BIDIR | AD(31-0) address and data bus (1.5-3.3V)             |  |  |

| PCIAD[22] | AH  | 18       | BIDIR | AD(31-0) address and data bus (1.5-3.3V)             |  |  |

| PCIAD[23] | AK  | 17       |       |                                                      |  |  |

| PCIAD[24] | AG  | 16       | BIDIR | AD(31-0) address and data bus (1.5-3.3V)             |  |  |

| PCIAD[25] | AK  | 16       | BIDIR | AD(31-0) address and data bus (1.5-3.3V)             |  |  |

| PCIAD[26] | AH  | 16       | BIDIR | AD(31-0) address and data bus (1.5-3.3V)             |  |  |

| <b>`</b>  |     |          | BIDIR | AD(31-0) address and data bus (1.5-3.3V)             |  |  |

| PCIAD[27] | AJ  | 16       | BIDIR | AD(31-0) address and data bus (1.5-3.3V)             |  |  |

| PCIAD[28] | AG  | 15       |       |                                                      |  |  |

#### Pin Assignment

| PIN NAME             | LOCATION TYP |         | TYPE  | DESCRIPTION                              |

|----------------------|--------------|---------|-------|------------------------------------------|

|                      |              |         | BIDIR | AD(31-0) address and data bus (1.5-3.3V) |

| PCIAD[29]            | AK           | 15      |       | (,                                       |

|                      |              |         | BIDIR | AD(31-0) address and data bus (1.5-3.3V) |

| PCIAD[3]             | AK           | 26      |       |                                          |

|                      |              |         | BIDIR | AD(31-0) address and data bus (1.5-3.3V) |

| PCIAD[30]            | AH           | 15      |       |                                          |

|                      | A 1          | 15      | BIDIR | AD(31-0) address and data bus (1.5-3.3V) |

| PCIAD[31]            | AJ           | 15      | BIDIR | AD(31-0) address and data bus (1.5-3.3V) |

| PCIAD[4]             | AH           | 26      | DIDIK |                                          |

| [ . ]                |              |         | BIDIR | AD(31-0) address and data bus (1.5-3.3V) |

| PCIAD[5]             | AJ           | 26      |       |                                          |

|                      |              |         | BIDIR | AD(31-0) address and data bus (1.5-3.3V) |

| PCIAD[6]             | AG           | 25      |       |                                          |

|                      |              |         | BIDIR | AD(31-0) address and data bus (1.5-3.3V) |

| PCIAD[7]             | AK           | 25      |       |                                          |

|                      |              | 24      | BIDIR | AD(31-0) address and data bus (1.5-3.3V) |

| PCIAD[8]             | AK           | 24      | BIDIR | AD(31-0) address and data bus (1.5-3.3V) |

| PCIAD[9]             | AH           | 24      | DIDIK |                                          |

|                      |              |         | BIDIR | C/BE Command Bus Byte Enables{1.5V-      |

| PCICBEN[0]           | AG           | 24      |       | 3.3v]                                    |

|                      |              |         | BIDIR | C/BE Command Bus Byte Enables{1.5V-      |

| PCICBEN[1]           | AK           | 22      |       | 3.3v]                                    |

|                      |              |         | BIDIR | C/BE Command Bus Byte Enables{1.5V-      |

| PCICBEN[2]           | AK           | 19      |       | 3.3v]                                    |

|                      | AG           | 17      | BIDIR | C/BE Command Bus Byte Enables{1.5V-      |

| PCICBEN[3]           | AG           | 17<br>8 | IN    | 3.3v]<br>Clk PciClk (3.3v)               |

| PCIClk<br>PCIDevSelN | AJ           | °<br>22 | BIDIR | DEVSEL# Device select[1.5V-3.3V]         |

| PCIFrameN            | AH           | 20      | BIDIR | Frame# Cycle Frame(3.3v)                 |

| PCIGntN              | AH           | 9       | IN    | Gnt# Grant (3.3v)                        |

| PCIIdSel             | AF           | 23      | IN    | Initialisation Device Select             |

| PCIIntAN             | AH           | 8       | OUT   | INTA# Interrupt A open drain             |

| PCIIRdyN             | AJ           | 20      | BIDIR | IRDY# Initiator ready (3.3v)             |

| PCIPar               | AH           | 22      | BIDIR | PAR Parity (3.3v)                        |

| PCIReqN              | AK           | 9       | OUT   | REQ# Request[3.3v]                       |

| PCIRstN              | AG           | 8       | IN    | RST# Reset (3.3v)                        |

| PCIStopN             | AG           | 21      | BIDIR | STOP# [3.3v]                             |

| PCITRdyN             | AH           | 21      | BIDIR | TRDY# Target Ready[3.3v]                 |

|                      | 7.41         |         | PWR   | PLL analogue ground = 0v (islolated from |

| PLLAG[0]             | AJ           | 7       |       | GND)                                     |

|                      |              |         | PWR   | PLL analogue ground = 0v (isolated from  |

| PLLAG[1]             | AJ           | 6       |       | GND)                                     |

|                      |              |         | PWR   | PLL analogue ground = 0v (isolated from  |

| PLLAG[2]             | AJ           | 5       |       | GND)                                     |

| PLLVAA[0]            | AH           | 7       | PWR   | PLL analogue power = 3.3v                |

| PLLVAA[1]            | AH           | 6       | PWR   | PLL analogue power 3.3v                  |

| PLLVAA[2]            | AH           | 5       | PWR   | PLL analogue power 3.3v                  |

| DefClir              | A 17         | c       | IN    | Alternative External Reference Clock     |

| RefClk               | AK           | 6       |       | signal                                   |

| PIN NAME    | LOC | LOCATION |       | DESCRIPTION                                                                       |  |  |

|-------------|-----|----------|-------|-----------------------------------------------------------------------------------|--|--|

| 00.01       |     | BIDIR    |       | Serial Bus Clk signal (Open Collector)<br>Controled from <u>ROMControl</u>        |  |  |

| SBClk       | AH  | 2        | BIDIR | register.<br>Serial Bus Data signal (Open Collector)<br>Controled from ROMControl |  |  |

| SBData      | AH  | 1        | IN    | register.<br>Production Test Mode Scan Enable signal                              |  |  |

| ScanEnable  | AF  | 7        |       |                                                                                   |  |  |

| SSTLVREF[0] | В   | 10       | IN    | Memory controller reference voltage<br>signal                                     |  |  |

|             |     |          | IN    | Memory controller reference voltage                                               |  |  |

| SSTLVREF[1] | B   | 22       | IN    | signal<br>Memory controller reference voltage                                     |  |  |

| SSTLVREF[2] | J   | 29       | IN    | signal<br>Memory controller reference voltage                                     |  |  |

| SSTLVREF[3] | AA  | 29       |       | signal                                                                            |  |  |

| Stereo      | AJ  | 4        | OUT   | Video Stereo signal                                                               |  |  |

| TestMode    | AF  | 6        | IN    | Production test global enable (Active high)                                       |  |  |

| VCC_DFP     | Р   | 1        | PWR   | 2.50vdc nominal                                                                   |  |  |

| VCC_DFP     | Р   | 4        | PWR   | 2.50vdc nominal                                                                   |  |  |

| VCC_DFP     | к   | 5        | PWR   | 2.50vdc nominal                                                                   |  |  |

| VCC_DFP     | G   | 1        | PWR   | 2.50vdc nominal                                                                   |  |  |

| VCC_DFP     | G   | 5        | PWR   | 2.50vdc nominal                                                                   |  |  |

| VDD_TTL     | AJ  | 1        | PWR   | 3.30vdc nominal                                                                   |  |  |

| VDD_TTL     | AJ  | 2        | PWR   | 3.30vdc nominal                                                                   |  |  |

| VDD_TTL     | AF  | 5        | PWR   | 3.30vdc nominal                                                                   |  |  |

| VDD_TTL     | AC  | 2        | PWR   | 3.30vdc nominal                                                                   |  |  |

| VDD_TTL     | AC  | 5        | PWR   | 3.30vdc nominal                                                                   |  |  |

| VDD_TTL     | W   | 5        | PWR   | 3.30 vdc nominal                                                                  |  |  |

| VDD_TTL     | U   | 1        | PWR   | 3.30vdc nominal                                                                   |  |  |

| VDD_TTL     | Р   | 5        | PWR   | 3.30vdc nominal                                                                   |  |  |

| VDD_TTL     | AF  | 8        | PWR   | 3.30vdc nominal                                                                   |  |  |

| VDD_TTL     | AK  | 7        | PWR   | 3.30vdc nominal                                                                   |  |  |

| VDD_TTL     | AK  | 2        | PWR   | 3.30vdc nominal                                                                   |  |  |

|             |     |          | PWR   | 3.30vdc nominal (1.50vdc nominal                                                  |  |  |

| VDDQ        | AH  | 28       |       | AGP4X)                                                                            |  |  |

|             |     |          | PWR   | 3.30vdc nominal (1.50vdc nominal                                                  |  |  |

| VDDQ        | AG  | 20       |       | AGP4X)                                                                            |  |  |

|             |     |          | PWR   | 3.30vdc nominal (1.50vdc nominal                                                  |  |  |

| VDDQ        | AF  | 16       | DWD   | AGP4X)                                                                            |  |  |

|             |     | 1.4      | PWR   | 3.30vdc nominal (1.50vdc nominal                                                  |  |  |

| VDDQ        | AH  | 14       | PWR   | AGP4X)<br>3.30vdc nominal (1.50vdc nominal                                        |  |  |

| VDDQ        | AF  | 9        | I WIX | AGP4X)                                                                            |  |  |

|             |     | 5        | BIDIR | DAC DDC Clk signal Head 0 (Open                                                   |  |  |

| VidADDCClk  | U   | 2        |       | collector)                                                                        |  |  |

|             |     |          | BIDIR | DAC DDC Data signal Head 0 (Open                                                  |  |  |

| VidADDCData | U   | 3        |       | collector)                                                                        |  |  |

| VidAHSync   | Р   | 2        | OUT   | DAC Horizontal Sync signal Head 0                                                 |  |  |

| VidAVSync    | Р  | 3 | OUT   | DAC Vertical Sync signal Head 0          |

|--------------|----|---|-------|------------------------------------------|

|              |    |   | BIDIR | Head 1 DDC Clk signal (Open Collector)   |

| VidBDDCClk   | V  | 2 |       |                                          |

|              |    |   | BIDIR | Head 1 DDC Data signal (Open Collector)  |

| VidBDDCData  | V  | 3 |       |                                          |

| VidBHSync    | N  | 4 | OUT   | DAC Horizontal Sync signal Head 1        |

| VidBVSync    | N  | 5 | OUT   | DAC Vertical Sync signal Head 1          |

|              |    |   | IN    | Dual Function:                           |

|              |    |   |       | DAC Horizontal Sync signal Head 1, and   |

|              |    |   |       | PCIClk 66MHz capable (Active High) -     |

| VidInData[0] | R  | 3 |       | see <u>Reset</u>                         |

|              |    |   | IN    | Dual Function:                           |

|              |    |   |       | Video Input Data signal, and             |

|              |    |   |       | Active High Boot from ROM                |

| VidInData[1] | R  | 4 |       | (UseROMConfig) – see Reset               |

|              |    |   | IN    | Dual Function:                           |

|              |    |   |       | Video Input Data signal, and             |

|              |    |   |       | Active High Board is AGP Type - see      |

| VidInData[2] | R  | 5 |       | Reset                                    |

| VidInData[3] | Т  | 1 | IN    | Video Input signal                       |

| VidInData[4] | т  | 2 | IN    | Video Input Data signal                  |

| VidInData[5] | т  | 3 | IN    | Video Input Data signal                  |

| VidInData[6] | Т  | 4 | IN    | Video Input Data signal                  |

| VidInData[7] | т  | 5 | IN    | Video Input signal                       |

|              |    |   | IN    | Video Input Data Strobe and Clock Source |

| VidInStrobe  | R  | 2 |       | signal                                   |

|              |    |   | BIDIR | External Reference Clock Source signal   |

| Xtal         | AK | 5 |       |                                          |

#### 8.5 Pinlist by Number

#### 8.6 Schematics

Please refer to the supplied PDF or ZIP file for P9 Typical Board Layouts and Data.

## **9** Memory

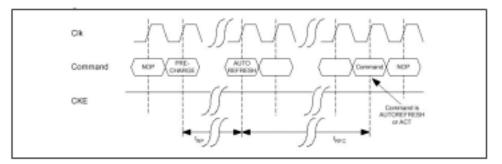

The P9 memory system is intended for use with Double Data Rate (DDR) Synchronous Dynamic Memories. The memories can be SGRAM or SDRAM devices. Configuration is via <u>memory control</u> registers in region 0.:

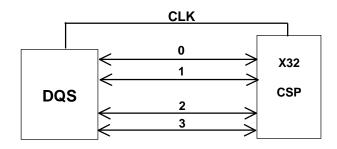

The system supports a 256 bit interface split into two 128 bit buses with replicated address and control lines. It can operate as a single 128 bit TQFP or CSP interface. Each interface has its own Address Bus, Control Signals and full register set.

#### 9.1 Strobe Setup

Strobes are supplied from memory on data transitions and repositioned to give sufficient data setup time using delay chains. There is a register bitfield which selectively delays each of the Incoming and Outgoing strobes and the Clock Out. For a typical clock delay chain register set see *P9 Reference Guide* volume II:

- MV0Clock

- MV0StrobeInvert

- <u>MV0StrobeOutDelay0</u>

- MV0StrobeOutDelay1

- <u>MV0StrobeInDelay0</u>, and

- <u>MV0StrobeInDelay1</u>

The system can be configured to use Strobe per Byte or Strobe per Device.

Note: There is no clock In delay

#### 9.1.1 DDR SDRAM

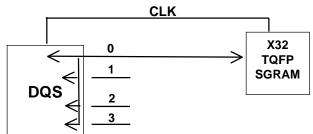

This configuration uses a full set of 4 individual strobes plus clock out. There is one delay register for each byte lane and controller. The memory device is a 32 bit CSP.

Figure 9.1 Non-common Strobes (DDR SDRAM)

#### 9.1.2 DDR SGRAM

For sigle-strobe devices the strobe is replicated internally on input to supply the 4 strobe lines. DDR SGRAMs are not frequently encountered because they tend to use arbitrary blockfill without support for byte masking.

Figure 9.2 Common Strobes (DDR SGRAM)

#### 9.1 System Parameters

The Memory System employs a comprehensive set of registers which allow for a wide range of memory configurations. The timing parameters used to control synchronous memories can be adjusted to allow for optimum performance depending on memory type, speed grade, data rate and the system clock frequency (MClk). Memory functionally can be enabled depending on the type fitted. Full addressing control is available so that virtually any memory configuration can be fitted.

The following parameters are used to control accesses to the memory. These values fall into three categories

- Addressing

- Functionality and Optimizations

- Timing and Mode

#### 9.1.1 Addressing

These parameters are specified in the **MemoryControl** and **MVCaps** registers.

Note: On P9 the Column Address is always 0

#### 9.1.2 Mode and Timing

These parameters are specified in the MVMode, MVCaps and delay chain registers registers.

#### 9.1.3 Mode

The mode register stores the data for controlling the various operating modes of the DDR SGRAM. It programs CAS latency, addressing mode, burst length, test mode, DLL Reset and various vendor specific options.

| Bits | Name        | Read | Write | Rese    | Description                                     |

|------|-------------|------|-------|---------|-------------------------------------------------|

| 02   | BL          | 1    | 1     | t<br>Ox | Burst Length always = 4 (must be 4 dwords)      |

| 02   | 52          | •    | •     | XXXX    |                                                 |

|      |             |      |       | XXX     |                                                 |

|      |             |      |       | X       |                                                 |

| 3    | BT          | 1    | 1     |         | Burst Type always = 0 (Sequential)              |

| 46   | CAS         | 1    | 1     |         | CAS Latency                                     |

| 7    | ТМ          | 1    | 1     |         | Test Mode                                       |

| 8    | DLL         | 1    | 1     |         | DLL Reset: 0= No, 1 = Yes                       |

| 911  | Reserved    | 1    | ×     |         | Reserved for future use                         |

| 12   | Mode        | 1    | 1     |         | Mode/Extended Mode: 0 = Mode, 1 =               |

|      |             |      |       |         | Extended Mode.                                  |

| 1315 | Reserved    | 1    | ×     |         |                                                 |

|      | Extended    | 1    | 1     |         | Bit pattern to load into extended mode register |

|      | Mode        |      |       |         | during initialization                           |

| 16   | DLL         | 1    | 1     |         | DLL Enable (should be set = 1)                  |

| 17   | DS0         | 1    | 1     |         | DriveStrength0: With DS1, sets drive            |

|      |             |      |       |         | strength and matched impedance mode.            |

| 1821 | Reserved    | 1    | ×     |         |                                                 |

| 22   | DS1         | 1    | 1     |         | See DS0                                         |

| 2327 | Reserved    | 1    | ×     |         |                                                 |

| 28   | Extended    | 1    | 1     |         | 0 = Mode                                        |

|      | Mode Access |      |       |         | 1 = Extended Mode                               |

#### 9.1.3.1 Burst Length

BL is always 4 dwords on P9

#### 9.1.3.2 Burst Type

Burst Type is Sequential (=0)

#### 9.1.3.3 CAS Latency (CL)

This parameter determines the CAS latency expected by the memory controller. The *CasLatency* parameter can be loaded directly with the appropriate value from the memory device data sheet plus 1. For example, if a CAS latency of 2 is required then the CasLatency parameter should be set to 3.

#### 9.1.4 Extended Mode Parameters

These fields control the DLL enables, Driver Impedance control (DIC) and QFC. DLL and DIC are enabled, QFC is disabled. See the <u>MVMode</u> register mask details.

#### 9.1.5 Memory Control

Refer to the MemoryControl register in Reference Guide Volume II for parameter information.

#### 9.1.6 MVTimingA

#### 9.1.6.1 Row Cycle (tRC)

The minimum time between Activate Commands to the same bank, calculated as tRC (in MClks) -1.

#### 9.1.6.2 RAS to CAS Write (tRCDWR)

The delay from an Activate Command to a Write Command, calculated as: tRCDWR (in MClks) -1.

#### 9.1.6.3 RAS to CAS Read (tRCDRD)